近日,由國家半導(dǎo)體照明工程研發(fā)及產(chǎn)業(yè)聯(lián)盟(CSA)與第三代半導(dǎo)體產(chǎn)業(yè)技術(shù)創(chuàng)新戰(zhàn)略聯(lián)盟(CASA)主辦,南方科技大學(xué)微電子學(xué)院與北京麥肯橋新材料生產(chǎn)力促進(jìn)中心有限公司共同承辦的第十七屆中國國際半導(dǎo)體照明論壇(SSLCHINA 2020)暨2020國際第三代半導(dǎo)體論壇(IFWS 2020)在深圳會展中心召開。

期間,由廣東芯聚能半導(dǎo)體有限公司,中電化合物半導(dǎo)體有限公司,英諾賽科(珠海)科技有限公司共同協(xié)辦的功率電子器件及封裝技術(shù)分會上,中山大學(xué)黎城朗分享凹槽深度對GaN槽柵型縱向?qū)ňw管電學(xué)特性的影響研究的最新進(jìn)展。

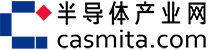

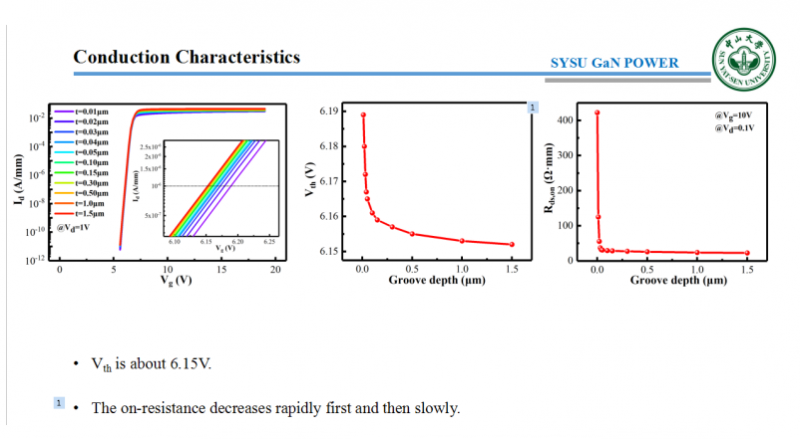

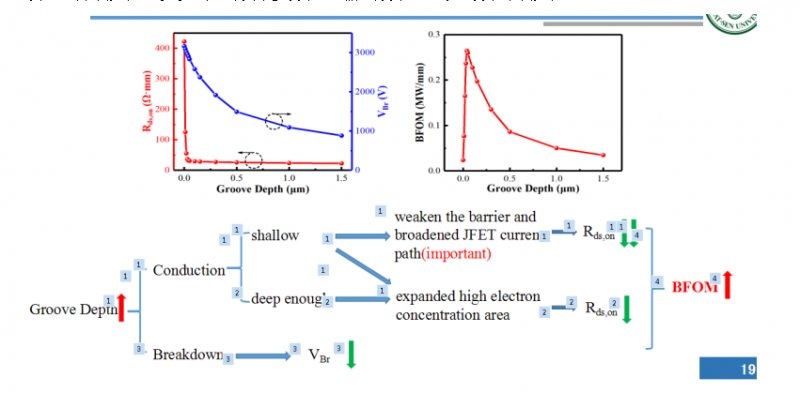

在這項(xiàng)工作中,對GaN縱向溝槽MOSFET的凹槽深度參數(shù)進(jìn)行了系統(tǒng)研究,以進(jìn)一步改善器件的導(dǎo)通特性。通過仿真探究了凹槽相對pGaN層的位置對導(dǎo)通時(shí)溝道下方漂移區(qū)的耗盡層勢壘峰的影響,以及對器件轉(zhuǎn)移特性、輸出特性和耐壓特性的影響。

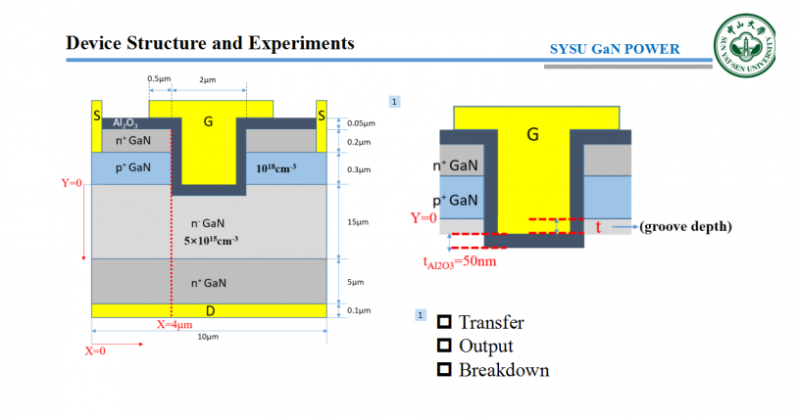

結(jié)果表明,凹槽深度的增加,可以削弱漂移區(qū)耗盡層勢壘峰對導(dǎo)電通道的影響,使凹槽下方縱向?qū)щ娡ǖ勒箤挘瑴p小導(dǎo)通電阻,而閾值電壓基本不變。在器件設(shè)計(jì)時(shí),需折中考慮凹槽深度增加導(dǎo)致的縱向?qū)щ娡ǖ勒箤捙c遷移率低下的凹槽界面積累區(qū)長度的增加對導(dǎo)通電阻的影響。這項(xiàng)仿真研究對高性能GaN縱向?qū)ú蹡牌骷Y(jié)構(gòu)設(shè)計(jì)具有一定的指導(dǎo)作用。

(內(nèi)容根據(jù)現(xiàn)場資料整理,如有出入敬請諒解)