解析適用于 SiC 柵極驅(qū)動的 PCB 布局方法

作者:Dave Skinner & Yuequan Hu

在為任一高功率或高電壓系統(tǒng)設(shè)計印刷電路板 (PCB) 布局時,柵極驅(qū)動電路特別容易受到寄生阻抗和信號的影響。對于碳化硅 (SiC) 柵極驅(qū)動,更需認(rèn)真關(guān)注細(xì)節(jié),因為其電壓和電流的轉(zhuǎn)換速率通常比硅快得多。遵循指定 PCB 設(shè)計指南,可以幫助減少這些常見隱患并消除實驗室或現(xiàn)場故障。

SiC 功率電路的優(yōu)點和注意事項

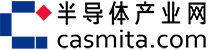

SiC 功率電子器件的主要優(yōu)點是開關(guān)頻率高、導(dǎo)通損耗低、效率更高且熱管理系統(tǒng)更簡單。與硅基轉(zhuǎn)換器相比,由于 SiC 功率系統(tǒng)具有這些優(yōu)勢,因此能夠在要求高功率密度的應(yīng)用(如太陽能逆變器、儲能系統(tǒng) (ESS)、不間斷電源 (UPS) 和電動汽車)中優(yōu)化性能。但是,由于高電壓轉(zhuǎn)換速率 (dv/dt) 和電流轉(zhuǎn)換速率 (di/dt) 是 SiC 功率器件的固有特性,使其與硅基電路相比,這些電路對串?dāng)_、誤導(dǎo)通、寄生諧振和電磁干擾 (EMI) 更為敏感。(圖 1)。

圖 1. 高電壓和電流轉(zhuǎn)換速率所產(chǎn)生影響的概要

將功率 MOSFET 并聯(lián)時,設(shè)計人員必須更密切地注意如何最大限度降低這些影響,因為器件之間的電流分配不均會影響性能。例如,在開關(guān)瞬變過程中,在并聯(lián)中增加一個器件會使 di/dt 倍增,從而可能導(dǎo)致更大的電壓過沖。此外,任何寄生電感都可能產(chǎn)生與反饋機(jī)制耦合的諧振,從而只會使電流不平衡的情況變得更糟。在這種情況下,PCB 設(shè)計人員必須特別注意要降低寄生電感。

電路板寄生現(xiàn)象對 SiC 電路的負(fù)面影響

SiC 電路中的寄生電感和電容

首先,SiC MOSFET 具有理想的固有低寄生電容(CGD、CDS、CGS)。這種特性支持高開關(guān)頻率,因此有助于實現(xiàn)高功率密度設(shè)計。但是,與這種好處如影隨形的是,在布局中不可避免地容易受到寄生電感諧振影響的情況。寄生電感本身可存在于應(yīng)用電路的柵極回路 (LGS) 和功率回路 (LDS) 以及共源極電感 (LCS) 之中。如之前所述,導(dǎo)致這些電感的因素包括走線長度很長,以及器件引線之間的電感。

柵極回路電感會增加?xùn)艠O電壓的振鈴,這反過來又會增加導(dǎo)通延遲,并且在某些情況下,會導(dǎo)致 MOSFET 的漏極-源極電壓發(fā)生振蕩振鈴。通常,應(yīng)最大限度地減小柵極回路電感以避免 MOSFET 的誤工作,但這種寄生電感的影響是三種主要寄生電感中最小的。

整個器件的過沖電壓通常由功率回路電感(有時也稱為開關(guān)回路電感)造成,而這會產(chǎn)生高開關(guān)損耗。共源極電感會在開關(guān)瞬變過程中產(chǎn)生對柵極驅(qū)動的電壓反饋,抵消柵極電壓的變化并減慢漏極電流,從而顯著增加導(dǎo)通和關(guān)斷時的開關(guān)損耗。[1] 此外,并聯(lián)器件之間微小的寄生 LCS 不匹配情況也會在開關(guān)瞬變過程中造成電流不平衡,從而放大負(fù)柵電壓反饋的影響。

設(shè)計 PCB 時,不可能完全消除所有寄生電感和電容。但是,一些常用技術(shù)可以幫助最大限度地減小這些電感和電容。

應(yīng)對 SiC 柵極驅(qū)動布局方面的挑戰(zhàn)

使功率曲線遠(yuǎn)離柵極回路

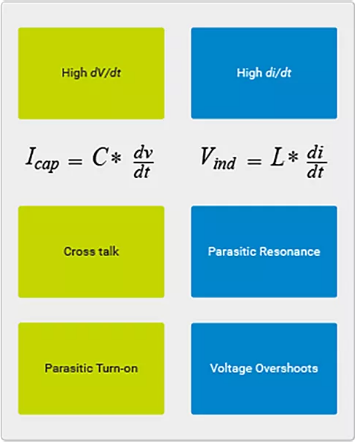

典型情況下,在單層 PCB 上布線的功率回路通常被稱為“橫向功率回路”。而第一個內(nèi)層用作“屏蔽層”,以減少功率回路中高開關(guān)頻率所產(chǎn)生的磁場的影響(圖 2)。功率回路中的脈沖電流在屏蔽層內(nèi)催生出電流和磁場,從而抵消功率回路中的電流和磁場。最終,由于有效地減小了功率回路和柵極驅(qū)動回路內(nèi)包含的面積,這將降低寄生電感。

最大限度縮短柵極驅(qū)動和 MOSFET 之間的距離

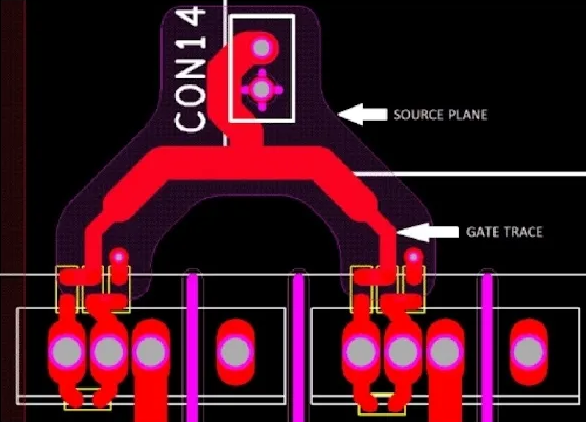

任一柵極回路電感都會與輸入電容產(chǎn)生諧振,并產(chǎn)生柵極-源極電壓振蕩,從而導(dǎo)致漏極-源極電壓振鈴。將柵極驅(qū)動放置在緊鄰 SiC MOSFET 的位置,以最小的走線長度將柵極回路電感降至最低。此外,這種做法還有助于使各并聯(lián) MOSFET 設(shè)計之間的共源極電感保持恒定。

以最小走線長度使 PCB 布局保持對稱

最大程度地縮短高頻率柵極回路和功率回路的周長,以減少電壓過沖和可能由該過沖引起的任何 EMI,是十分關(guān)鍵的。這對于并聯(lián)器件尤其重要,因為寄生電感本來就更高。如圖 2 所示,用于并聯(lián) MOSFET 的對稱柵極驅(qū)動路徑可實現(xiàn)更均勻的電流分布。

圖 2. 通過消除電流回路中的磁場并進(jìn)行對稱走線布局,以降低寄生電感的影響

將小電容器置于柵極和源極之間

與硅基電路相同,通過在柵極和源極之間放置去耦電容器,可以最大限度地減少由瞬態(tài)信號引起的柵極電壓尖峰。該電容為柵極驅(qū)動電流提供一個低阻抗路徑,從而減小 VGS 的升幅。但這會減慢柵極驅(qū)動信號,從而增加開關(guān)損耗。因此,應(yīng)調(diào)整 CGS 的值以平衡損耗和瞬態(tài)抗擾度。

增加 EMI 濾波器或緩沖器

可以通過增加 RC 緩沖器或鐵氧體磁珠等組件來實現(xiàn)有效的 EMI 抑制。沿(漏極和源極之間的)DC 總線連接的 RC 緩沖器將吸收漏極處的寄生振鈴或電壓過沖。在高頻率下,與柵極串聯(lián)放置的高電阻、低電感鐵氧體磁珠,可有效抑制柵極處的寄生諧振。此寄生振蕩由漏極-源極電壓瞬變引起,該瞬變在柵極電路上生成電壓,有可能會在柵極引腳處的電容和寄生電感(LC 諧振腔)之間引起諧振。鐵氧體磁珠可抑制這種振蕩,而不會對開關(guān)性能產(chǎn)生負(fù)面影響。

對于基于 SiC 的布局需要額外注意的事項

SiC 基功率電子器件的布局方法在許多方面類似于硅基電路。在這些布局操作中要格外小心,才能最終解決快速開關(guān)功率器件的各類問題挑戰(zhàn),使得設(shè)計人員能夠在其功率應(yīng)用中充分利用 SiC 的所有優(yōu)點。

參考資料

[1]. Z. Chen, D. Boroyevich and R. Burgos, "Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics," The 2010 International Power Electronics Conference - ECCE ASIA -, Sapporo, 2010, pp. 164-169, doi: 10.1109/IPEC.2010.5543851.