原文鏈接:https://www.imec-int.com/en/articles/monolithic-integration-gan-components-boosts-power-integrated-circuits

幾十年來(lái),硅基功率晶體管(MOSFET、場(chǎng)效應(yīng)晶體管)構(gòu)成了功率轉(zhuǎn)換系統(tǒng)的支柱,可將交流電 (AC) 轉(zhuǎn)換為直流電 (DC),反之亦然,或?qū)⒅绷麟姀牡蛪恨D(zhuǎn)換為高壓。在尋求可以提高開(kāi)關(guān)速度的替代品時(shí),氮化鎵 (GaN) 迅速成為領(lǐng)先的候選材料之一。GaN/AlGaN 材料體系表現(xiàn)出更高的電子遷移率和更高的擊穿臨界電場(chǎng)。結(jié)合高電子遷移率晶體管 (HEMT) 架構(gòu),與同類硅解決方案相比,它使器件和 IC 具有更高的擊穿強(qiáng)度、更快的開(kāi)關(guān)速度、更低的電導(dǎo)損耗和更小的占位面積。

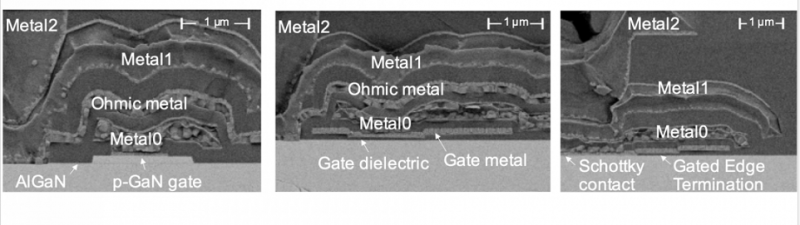

IMEC 200V GaN-on-SOI 功率 IC 技術(shù)和組件的橫截面示意圖。該工藝具有 E/D 模式 HEMT、肖特基二極管、電阻器、電容器的單片共集成,并包括先進(jìn)的工藝模塊(深溝槽隔離、襯底接觸、再分布層......)

今天,大多數(shù) GaN 電源系統(tǒng)由多個(gè)芯片組成?;?GaN 的器件在組裝到印刷電路板上之前作為分立元件組裝。這種方法的缺點(diǎn)是存在影響器件性能的寄生電感。“以驅(qū)動(dòng)器為例,在單獨(dú)的芯片上帶有驅(qū)動(dòng)器的分立晶體管受到驅(qū)動(dòng)器輸出級(jí)和晶體管輸入之間以及半橋開(kāi)關(guān)節(jié)點(diǎn)之間的寄生電感的影響。GaN HEMT 具有非常高的開(kāi)關(guān)速度,當(dāng)寄生電感未被抑制時(shí),這會(huì)導(dǎo)致振鈴(ringing),即信號(hào)的不希望的振蕩。減少寄生效應(yīng)和利用 GaN 卓越開(kāi)關(guān)速度的最佳方法是將驅(qū)動(dòng)器和 HEMT 集成在同一芯片上,”來(lái)自IMEC的Stefaan Decoutere 解釋道。

“同時(shí),它減少了半橋中兩個(gè)晶體管之間的死區(qū)時(shí)間控制,其中一個(gè)晶體管必須在另一個(gè)晶體管打開(kāi)時(shí)關(guān)閉。在這期間,電源和地之間存在短路,或死區(qū)時(shí)間。在芯片上集成所有組件將解決振鈴問(wèn)題,減少死區(qū)時(shí)間,并最終提高轉(zhuǎn)換器的電源效率。”

d 模式 HEMT 的共集成

Imec 已經(jīng)在絕緣體上硅 (SOI) 基板上單片集成構(gòu)建塊(例如驅(qū)動(dòng)器、半橋和控制/保護(hù)電路)取得了巨大進(jìn)展?,F(xiàn)在,研究人員已經(jīng)成功地在產(chǎn)品組合中添加了兩個(gè)廣受歡迎的組件:d 模式(耗盡模式)HEMT 和肖特基二極管。

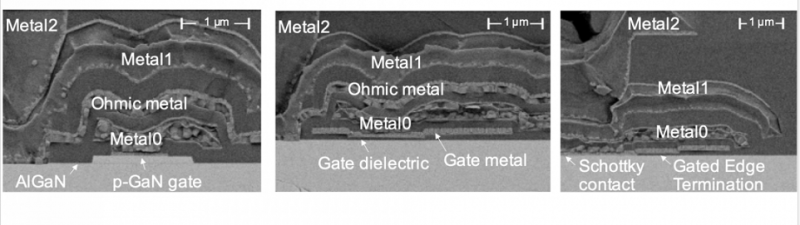

在 200 mm GaN-on-SOI 襯底上制造的高壓組件的工藝橫截面 (a) e 模式 pGaN-HEMT (b) d 模式 MIS-HEMT,(c) 肖特基勢(shì)壘二極管。所有器件都包括基于前端和互連金屬層并由介電層隔開(kāi)的金屬場(chǎng)板

提高 GaN 功率 IC 的全部性能的主要障礙之一仍然是尋找合適的解決方案來(lái)解決 GaN 中缺乏具有可接受性能的 p 溝道器件的問(wèn)題。CMOS 技術(shù)使用互補(bǔ)且更對(duì)稱的 p 型和 n 型 FET 對(duì),基于兩種 FET 的空穴和電子遷移率。然而,在 GaN 中,空穴的遷移率比電子的遷移率差 60 倍左右;在硅中,這只是 2 倍。這意味著以空穴為主要載流子的 p 溝道器件將比 n 溝道對(duì)應(yīng)器件大 60 倍,而且效率極低。一種廣泛使用的替代方法是用電阻器代替 P-MOS。電阻晶體管邏輯 (RTL) 已用于 GaN IC,但在開(kāi)關(guān)時(shí)間和功耗之間表現(xiàn)出權(quán)衡。

“我們通過(guò)在 SOI 上的功能性 e-mode HEMT 平臺(tái)上共同集成 d-mode HEMTS,提高了 GaN IC 的性能。增強(qiáng)和耗盡模式是指在零源電壓下的 ON(d 模式)或 OFF(e 模式)狀態(tài),導(dǎo)致晶體管中的電流流動(dòng)(或不流動(dòng))。我們期望從 RTL 向直接耦合 FET 邏輯邁出一步將提高速度并降低電路的功耗,”Stefaan Decoutere 說(shuō)。

具有低泄漏電流的肖特基二極管

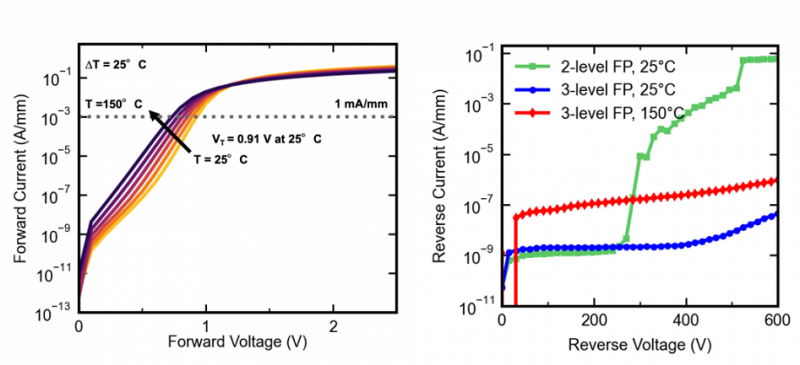

肖特基勢(shì)壘二極管的集成進(jìn)一步提高了 GaN 功率 IC 的功率效率。與硅二極管相比,它們可以在相同的導(dǎo)通電阻下承受更高的電壓,或者在相同的擊穿電壓下承受更低的導(dǎo)通電阻。“制造肖特基勢(shì)壘二極管的挑戰(zhàn)是獲得低導(dǎo)通電壓和低泄漏水平。不幸的是,當(dāng)您瞄準(zhǔn)較低的導(dǎo)通電壓時(shí),您最終會(huì)遇到一個(gè)小的屏障來(lái)阻止泄漏電流。肖特基二極管因漏電流高而臭名昭著。與傳統(tǒng) GaN 肖特基勢(shì)壘二極管相比,Imec 專有的柵極邊緣端接肖特基勢(shì)壘二極管架構(gòu) (GET-SBD) 可實(shí)現(xiàn)約 0.8 伏的低開(kāi)啟電壓,同時(shí)將漏電流降低幾個(gè)數(shù)量級(jí),

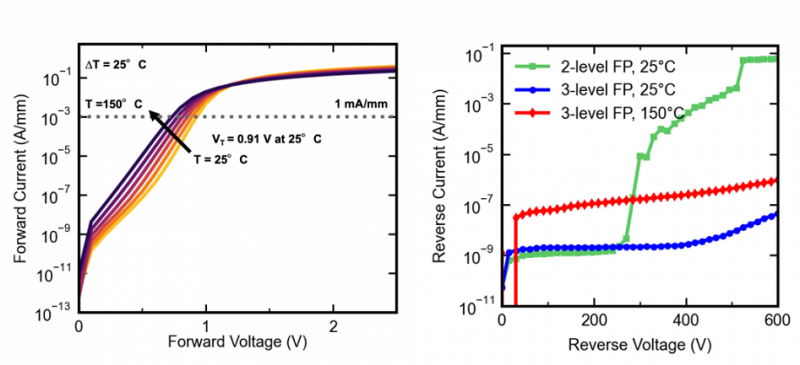

制造的 GET-SBD 的特性顯示(左)在 25°C 下以半對(duì)數(shù)刻度顯示 0.91V 的低開(kāi)啟電壓,以及(右)兩種不同陽(yáng)極的低反向漏電流(25°C 時(shí)為 2 nA/mm)在 25 和 150°C 下評(píng)估的場(chǎng)板配置。

快速開(kāi)關(guān)和高電壓

GaN 是高功率應(yīng)用的首選材料,因?yàn)閷?dǎo)致晶體管擊穿的臨界電壓(擊穿電壓)比硅高 10 倍。但對(duì)于低功率應(yīng)用,GaN 仍然具有優(yōu)于硅的優(yōu)勢(shì),因?yàn)樗哂谐錾拈_(kāi)關(guān)速度。“我們創(chuàng)建的基于 GaN 的 IC 為更小、更高效的 DC/DC 轉(zhuǎn)換器和負(fù)載點(diǎn) (PoL) 轉(zhuǎn)換器開(kāi)辟了道路。例如,智能手機(jī)、平板電腦或筆記本電腦包含可在不同電壓下工作的芯片,因此它們需要 AC/DC 轉(zhuǎn)換器來(lái)為電池充電,并需要設(shè)備內(nèi)部的 PoL 轉(zhuǎn)換器來(lái)產(chǎn)生不同的電壓。這些組件不僅包括開(kāi)關(guān),還包括變壓器、電容器和電感器。晶體管開(kāi)關(guān)速度越快,這些組件就越小,

Stefaan Decoutere:“快速充電器構(gòu)成了當(dāng)今 GaN 的最大市場(chǎng),其次是用于服務(wù)器、汽車(chē)行業(yè)和可再生能源的電源。預(yù)計(jì)使用 GaN 的電源在系統(tǒng)級(jí)更可靠。它們的外形尺寸和重量更小,從而減少了材料清單,從而降低了成本。

正在研究的垂直設(shè)備

“我們將專注于提高現(xiàn)有平臺(tái)的性能,并進(jìn)行進(jìn)一步的可靠性測(cè)試。我們目前提供用于原型設(shè)計(jì)的 200V 和 650V 平臺(tái),很快就會(huì)推出 100V。對(duì)于具有集成組件的 GaN-IC,1200V 大功率平臺(tái)可能不會(huì)產(chǎn)生顯著的改進(jìn)。電壓越高,組件變得越慢。因此,可能沒(méi)有必要在芯片上集成驅(qū)動(dòng)程序;模擬會(huì)告訴我們。”

“與此同時(shí),我們正在尋找分立 1200V 器件的替代品,使 GaN 技術(shù)能夠用于電動(dòng)汽車(chē)等最高電壓功率應(yīng)用。具有橫向拓?fù)涞木w管是當(dāng)今占主導(dǎo)地位的 GaN 器件架構(gòu)。這些器件的三個(gè)端子(源極、柵極和漏極)位于同一平面的表面,因此電場(chǎng)是橫向的,跨越 GaN 緩沖層和部分后端(金屬化、氧化物)。在垂直器件中,源極和柵極位于表面,而漏極位于外延疊層的底部。在這種情況下,電場(chǎng)流過(guò)整個(gè)堆棧。決定器件擊穿電壓的是源漏分離,較大的分離可以保護(hù)通道不被擊穿。然而,橫向放置的源極和漏極之間的距離越大,器件越大。因?yàn)?1200V 設(shè)備的芯片會(huì)變得太大,橫向架構(gòu)通常建議最高 650V。相反,對(duì)于垂直器件,使用更高的電壓歸結(jié)為創(chuàng)建更厚的外延堆疊,因?yàn)樵礃O和漏極位于堆疊的不同端。芯片的表面積沒(méi)有增加,”Stefaan Decoutere 總結(jié)道。