繼4月5日公開“一種芯片堆疊封裝及終端設(shè)備”專利后,華為技術(shù)有限公司近日又公開了2項芯片相關(guān)的發(fā)明專利。

△Source:國家知識產(chǎn)權(quán)局網(wǎng)站截圖

5月6日,國家知識產(chǎn)權(quán)局官網(wǎng)公開了華為申請的2項芯片相關(guān)專利——“一種多芯片堆疊封裝及制作方法”和“芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備”,申請公布號分別為CN114450785A和CN114450786A。

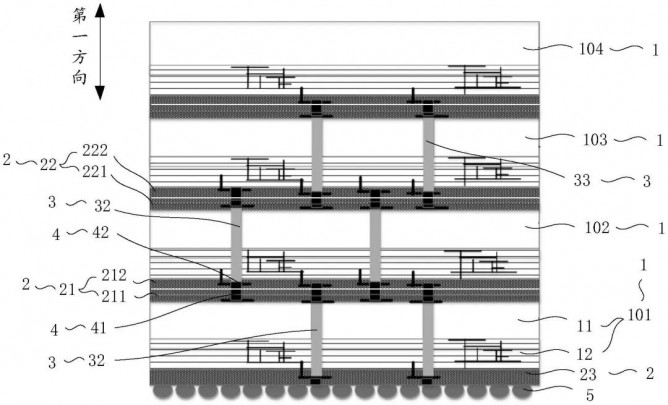

“一種多芯片堆疊封裝及制作方法”

該專利涉及芯片技術(shù)領(lǐng)域,不僅能夠解決多芯片的應(yīng)力集中問題,還能夠以進行更多層芯片的堆疊。

△Source:國家知識產(chǎn)權(quán)局網(wǎng)站截圖

該多芯片堆疊封裝包括:

沿第一方向堆疊設(shè)置的第一芯片(101)和第二芯片(102),其中所述第一芯片(101)內(nèi)沿所述第一方向開設(shè)有第一導(dǎo)電通孔(31),所述第二芯片(102)內(nèi)沿所述第一方向開設(shè)有第二導(dǎo)電通孔(32);

設(shè)置于所述第一芯片(101)和所述第二芯片(102)之間的第一再布線層(21),且所述第一再布線層(21)的兩側(cè)分別與所述第一芯片(101)的表面和所述第二芯片(102)的表面固定,其中所述第一導(dǎo)電通孔(31)和所述第二導(dǎo)電通孔(32)通過所述第一再布線層(21)導(dǎo)通,所述第一導(dǎo)電通孔(31)和所述第二導(dǎo)電通孔(32)錯開設(shè)置。所述多芯片堆疊封裝及制作方法用于芯片的制造。

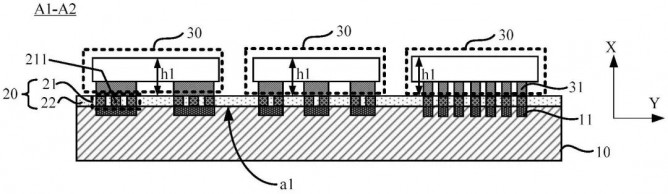

“芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備”

該專利為一種芯片堆疊封裝結(jié)構(gòu)(100)及其封裝方法、電子設(shè)備(1),涉及電子技術(shù)領(lǐng)域,用于解決如何將多個副芯片堆疊單元(30)可靠的鍵合在同一主芯片堆疊單元(10)上的問題。

△Source:國家知識產(chǎn)權(quán)局網(wǎng)站截圖

芯片堆疊封裝結(jié)構(gòu)(100),包括:

主芯片堆疊單元(10),具有位于第一表面上的絕緣且間隔設(shè)置的多個主管腳(11);

第一鍵合層(20),設(shè)置于第一表面上;第一鍵合層(20)包括絕緣且間隔設(shè)置的多個鍵合組件(21);

多個鍵合組件(21)中的每個包括至少一個鍵合部(211),任意兩個鍵合部(211)絕緣設(shè)置,且任意兩個鍵合部(211)的橫截面積相同;

多個鍵合組件(21)分別與多個主管腳(11)鍵合;

多個副芯片堆疊單元(30),設(shè)置于第一鍵合層(20)遠離主芯片堆疊單元(10)一側(cè)的表面;

副芯片堆疊單元(30)具有絕緣且間隔設(shè)置的多個微凸點(31);

多個微凸點(31)中的每個與多個鍵合組件(21)中的一個鍵合。

堆疊技術(shù)競爭激烈 臺積電/三星/英特爾等火力全開

據(jù)了解,3D堆疊技術(shù)是利用堆疊技術(shù)或通過互連和其他微加工技術(shù)在芯片或結(jié)構(gòu)的Z軸方向上形成三維集成,信號連接以及晶圓級,芯片級和硅蓋封裝具有不同的功能,針對包裝和可靠性技術(shù)的三維堆疊處理技術(shù)。

該技術(shù)用于微系統(tǒng)集成,是在片上系統(tǒng)(SOC)和多芯片模塊(MCM)之后開發(fā)的先進的系統(tǒng)級封裝制造技術(shù)。

當前,臺積電、英特爾、三星等國際半導(dǎo)體廠商都開發(fā)了自己的3D芯片封裝技術(shù)。

例如,英特爾于2018年底推出了業(yè)界首創(chuàng)的3D邏輯芯片封裝技術(shù)——Foveros;三星在2018年推出了名為“X-Cube”的3D IC封裝技術(shù);臺積電則將旗下SoIC、InFO及CoWoS等3D IC技術(shù)平臺進行整合,并命名為“3D Fabric”。

今年3月初,蘋果發(fā)布了迄今為止最強大的芯片——M1 Ultra,該芯片整合了兩塊M1 Max芯片,包含高達1140億個晶體管,而這也再次說明了先進封裝技術(shù)方向的正確性。

在芯片堆疊封裝領(lǐng)域,面對高手林立的競爭者,華為似乎也早已加入“戰(zhàn)局”。

緩解成本壓力 華為公開芯片堆疊封裝專利

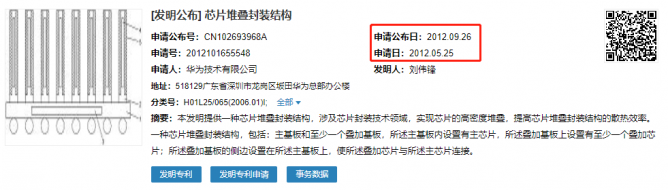

信息顯示,華為此次公開的2項專利申請時間均為2019年。而事實上,早在2012年,華為便向國家知識產(chǎn)權(quán)局申請了一項名為“芯片堆疊封裝結(jié)構(gòu)”的發(fā)明專利。這意味著,華為對芯片堆疊封裝的研究在2012年甚至更早的時間就已開始。

△Source:國家知識產(chǎn)權(quán)局網(wǎng)站截圖

今年3月底,華為首次公開確認芯片堆疊技術(shù)。

華為輪值董事長郭平在3月28日舉行的華為2021年年報發(fā)布會上表示,未來華為可能會采用多核結(jié)構(gòu)的芯片設(shè)計方案,以提升芯片性能,同時采用面積換性能,用堆疊換性能,使得不那么先進的工藝也能持續(xù)讓華為在未來的產(chǎn)品里面,能夠具有競爭力。

幾天后(4月5日),華為正式公開了“一種芯片堆疊封裝及終端設(shè)備”專利,涉及半導(dǎo)體技術(shù)領(lǐng)域,其能夠在保證供電需求的同時,解決因采用硅通孔技術(shù)而導(dǎo)致的成本高的問題。