在過(guò)去的57年中,摩爾定律一直是指導(dǎo)半導(dǎo)體行業(yè)發(fā)展的黃金法則。即使驅(qū)動(dòng)摩爾定律生效的條件正在發(fā)生改變,它也將繼續(xù)指引行業(yè)前行。

1965年,時(shí)任仙童半導(dǎo)體公司研發(fā)總監(jiān)的戈登•摩爾撰寫(xiě)了一篇關(guān)于未來(lái)10年內(nèi)半導(dǎo)體芯片發(fā)展趨勢(shì)的文章,對(duì)當(dāng)時(shí)芯片生產(chǎn)的技術(shù)能力和經(jīng)濟(jì)效益進(jìn)行了大膽預(yù)測(cè):

“在最小成本的前提下,單個(gè)芯片上的元器件數(shù)量基本上是每一年翻一倍。并且至少在未來(lái)十年保持這個(gè)增長(zhǎng)速度,到1975年單個(gè)芯片上將集成65,000個(gè)元器件。”

這一預(yù)測(cè)實(shí)際上也是對(duì)當(dāng)時(shí)半導(dǎo)體行業(yè)驚人的發(fā)展速度的真實(shí)寫(xiě)照。不過(guò),摩爾本人后來(lái)形容這是“一個(gè)大膽的推斷”。但就是這樣的一個(gè)推斷,在半導(dǎo)體行業(yè)不斷的變革中得到了多次證實(shí),同時(shí),業(yè)內(nèi)人士也在此基礎(chǔ)上不斷對(duì)其進(jìn)行延伸。

雖然摩爾定律成功指引了半導(dǎo)體行業(yè)發(fā)展,但事實(shí)上,它從來(lái)就不是科學(xué)意義上的一則真正“定律”。誠(chéng)然,它描述了半導(dǎo)體行業(yè)發(fā)展中取得的一系列令人印象深刻的成就,但它的預(yù)測(cè)更像是半導(dǎo)體行業(yè)寄予自己的一個(gè)雄心勃勃的目標(biāo)或路線(xiàn)圖。它之所以被廣泛采用,更多的是芯片制造商出于經(jīng)濟(jì)原因——希望芯片的功能能以一個(gè)可承受的價(jià)格來(lái)實(shí)現(xiàn)——而不是基于任何物理原理。

一個(gè)不斷變化的常數(shù)

在過(guò)去的50多年里,摩爾定律不斷演進(jìn)。摩爾關(guān)于以最小成本制造復(fù)雜芯片的最初預(yù)測(cè),也在演進(jìn)過(guò)程中被轉(zhuǎn)述成各種各樣的表述,現(xiàn)在這個(gè)定律最常被表述為半導(dǎo)體芯片可容納的晶體管數(shù)量呈倍數(shù)增長(zhǎng)。

這一速度隨著行業(yè)和技術(shù)的進(jìn)步而不斷變化。1975年,摩爾修正了自己的預(yù)測(cè):晶體管數(shù)量翻倍的時(shí)間從最初的一年上升到兩年。盡管增速有所減緩,但摩爾定律作為半導(dǎo)體行業(yè)飛速發(fā)展的本質(zhì)指引仍具有重要意義。

讓芯片再小一些

摩爾認(rèn)為,增加芯片面積、縮小元件尺寸以及優(yōu)化器件電路設(shè)計(jì)是實(shí)現(xiàn)晶體管數(shù)量翻倍的三個(gè)重要因素。

元件尺寸縮小在很大程度上是由光刻工藝和技術(shù)的發(fā)展推動(dòng)的。在過(guò)去的幾十年里,光刻技術(shù)的發(fā)展經(jīng)歷了減小曝光波長(zhǎng) (UV光),增加投影物鏡的數(shù)值孔徑 (NA),同時(shí)引入浸潤(rùn)式光刻技術(shù),以及多重圖形技術(shù)等。

光刻技術(shù)的進(jìn)步使得制作出更小尺寸芯片成為現(xiàn)實(shí),芯片制造商可以在同樣大小的晶圓上封裝更多的晶體管,使芯片性能得以增強(qiáng),同時(shí)保持低廉成本。而芯片尺寸的不斷縮小也正是半導(dǎo)體行業(yè)在過(guò)去40多年的時(shí)間里一直遵循摩爾定律的體現(xiàn)。

摩爾定律的盡頭?

更小的晶體管運(yùn)行速度更快,所需功率更小,因此,摩爾定律已經(jīng)成為不斷提高芯片性能和能效的代名詞。然而,當(dāng)芯片縮小到一定的程度,過(guò)小的尺寸勢(shì)必會(huì)對(duì)晶體管的工作產(chǎn)生影響,進(jìn)而打破了尺寸、性能和功耗之間的平衡。

目前,大多數(shù)芯片中使用的晶體管類(lèi)型在2000年代中期接近了這個(gè)臨界點(diǎn)。雖然晶體管仍在持續(xù)變小,但由此帶來(lái)的芯片性能的改善卻逐漸趨緩。

探索新的前進(jìn)道路

不過(guò),正如摩爾在1975年所說(shuō)的那樣,制造更小的尺寸只是提高芯片性能的一種方法。幾十年來(lái),半導(dǎo)體行業(yè)還通過(guò)元件和電路的巧妙設(shè)計(jì)——用于制造晶體管的材料和結(jié)構(gòu)的創(chuàng)新——提升了芯片性能。這種方法被稱(chēng)為“設(shè)計(jì)縮放”。例如,使用 “低介電常數(shù)材質(zhì)”等材料可以改善晶體管的電氣性能。

與此同時(shí),新的晶體管架構(gòu)源源不斷地被開(kāi)發(fā)出來(lái),以克服傳統(tǒng)晶體管的尺寸限制。為此,業(yè)界引入FinFETs技術(shù),將晶體管的柵極由平面結(jié)構(gòu)改成立體結(jié)構(gòu)。它也是首個(gè)被稱(chēng)為3D晶體管的新型晶體管。

尺寸和元件的縮放涉及晶體管本身的演變。近年來(lái),芯片性能的提高也是通過(guò)系統(tǒng)層面的創(chuàng)新實(shí)現(xiàn)的,即允許使用現(xiàn)有的晶體管技術(shù)來(lái)進(jìn)一步擴(kuò)展。

實(shí)現(xiàn)這一目標(biāo)的方法之一是通過(guò)更大的片上集成,如將處理器、存儲(chǔ)器和輔助功能整合到一個(gè)芯片上的片上系統(tǒng)解決方案,以及3D NAND閃存,即在同一區(qū)域內(nèi)制造多層閃存以增加存儲(chǔ)容量。另一個(gè)選擇是依靠先進(jìn)封裝技術(shù)將更多的優(yōu)化功能模塊集成在一起。

未來(lái)的十年

在過(guò)去的15年里,這些創(chuàng)新方法使摩爾定律依然生效且狀況良好。從整個(gè)行業(yè)的發(fā)展路線(xiàn)來(lái)看,它們將在未來(lái)十年甚至更長(zhǎng)時(shí)間內(nèi)讓摩爾定律繼續(xù)保持這種勢(shì)頭。

當(dāng)然,在元件方面,目前的技術(shù)創(chuàng)新足夠?qū)⑿酒闹瞥掏七M(jìn)至至少1納米節(jié)點(diǎn),其中包括gate-all-around FETs,nanosheet FETs,forksheet FETs,以及complementary FETs等諸多前瞻技術(shù)。此外,光刻系統(tǒng)分辨率的改進(jìn)(預(yù)計(jì)每6年左右縮小2倍)和邊緣放置誤差(EPE)對(duì)精度的衡量也將進(jìn)一步推動(dòng)芯片尺寸縮小的實(shí)現(xiàn)。

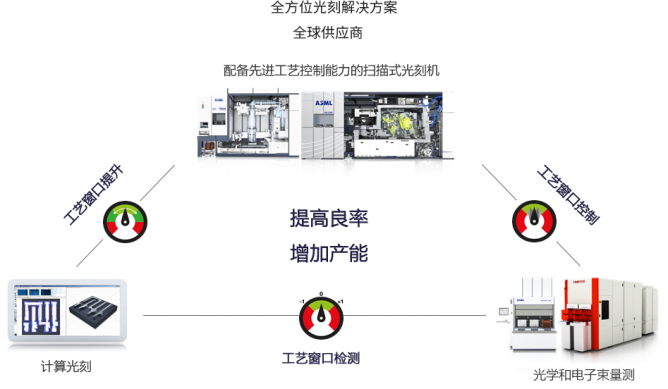

ASML作為半導(dǎo)體行業(yè)的引領(lǐng)者之一,始終為行業(yè)提供創(chuàng)新支持。我們的EPE路線(xiàn)圖是全方位光刻技術(shù)的關(guān)鍵,它將通過(guò)不斷改進(jìn)光刻系統(tǒng)和發(fā)展應(yīng)用產(chǎn)品(包括量測(cè)和檢測(cè)系統(tǒng))來(lái)實(shí)現(xiàn)。

此外,我們預(yù)計(jì)系統(tǒng)級(jí)的擴(kuò)展將發(fā)揮更大的作用:去年,存儲(chǔ)器制造商生產(chǎn)了176個(gè)存儲(chǔ)層疊加的3D NAND芯片,并宣布到2030年左右將生產(chǎn)超過(guò)600個(gè)存儲(chǔ)層的芯片路線(xiàn)圖。如果說(shuō)摩爾定律57年的歷史向我們展示了什么,那就是半導(dǎo)體行業(yè)充滿(mǎn)了新發(fā)展的想法。

只要我們還有想法,摩爾定律就會(huì)繼續(xù)生效!