以碳化硅(SiC)和氮化鎵(GaN)為代表的第三代半導體(亦稱寬禁帶半導體)材料具有禁帶寬度大、擊穿電場高、熱導率高、電子飽和速率高以及抗輻射能力強等優(yōu)點。其中SiC功率器件及模塊已經(jīng)逐漸成為特高壓柔性電網(wǎng)、5G移動通信基礎設施、高速軌道交通、新能源汽車、航空航天裝備、數(shù)據(jù)中心等“新基建”核心領域的“關鍵核芯”。

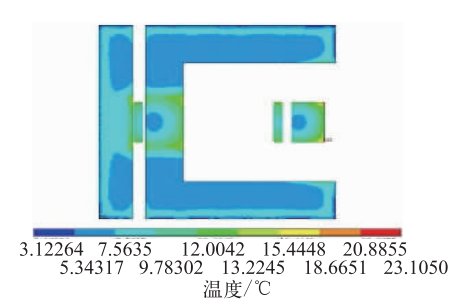

(a) 模擬芯片散熱情況

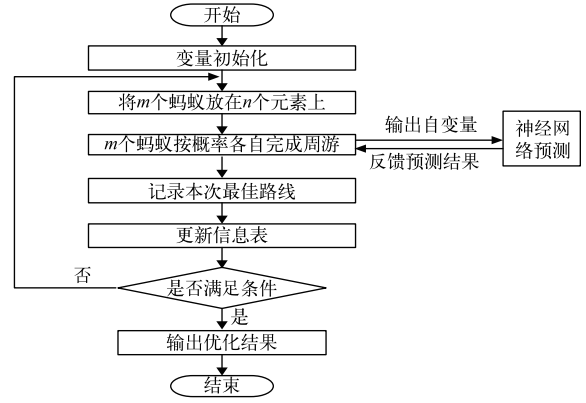

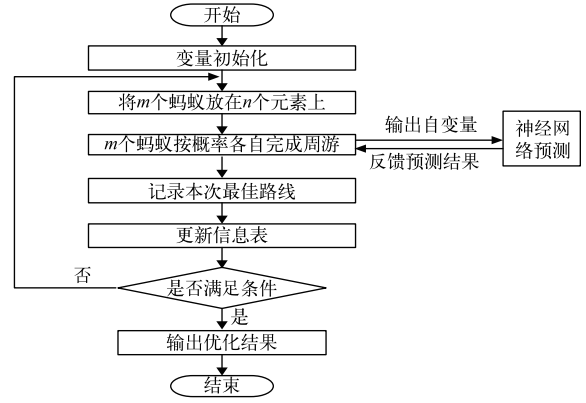

(e) ACO-BPNN流程圖

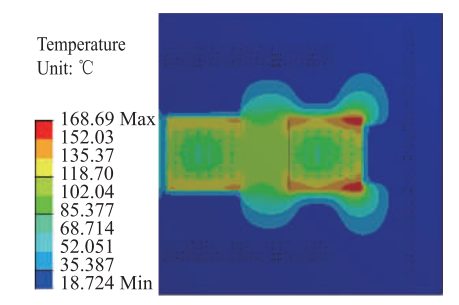

傳統(tǒng)SiC功率模塊封裝仍以鋁線鍵合互連為首選互連技術,然而鋁線鍵合的寄生電感大(大于10 nH),開關損耗高,熱失配引起的應力失效率高,這些都極大地限制了SiC功率器件的性能和可靠性。對于多芯片并聯(lián)的SiC超級結器件來說,開發(fā)多層平面互連的高密度集成化封裝技術是提高其性能和可靠性的必然途徑。隨著高密度集成化封裝的發(fā)展,其電-熱-磁-應力可靠性等技術難題也顯得愈發(fā)突出。為了保證功率器件的性能和可靠性,需要研究高密度集成封裝的多物理場耦合作用規(guī)律和優(yōu)化方法。

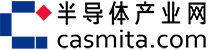

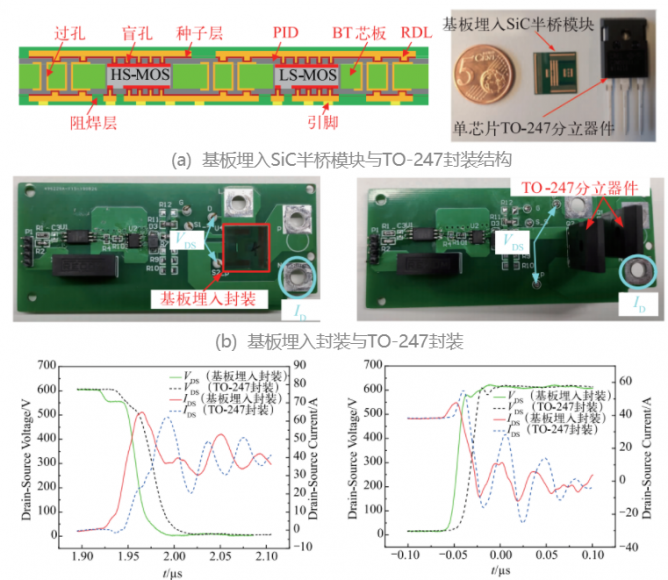

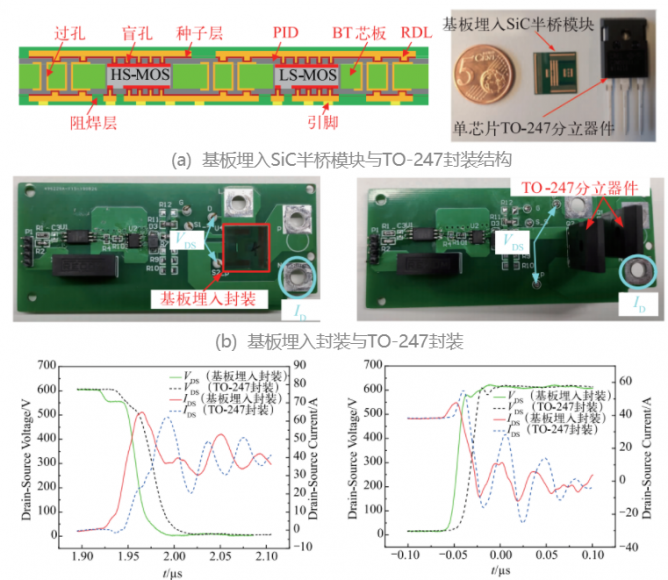

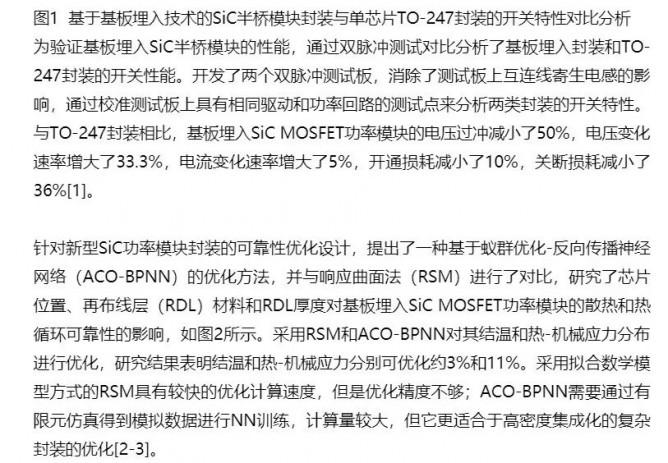

中科院微電子所侯峰澤副研究員和復旦大學樊嘉杰青年研究員提出了一種基于基板埋入技術的新型SiC功率模塊封裝及可靠性優(yōu)化設計方法:采用新型光敏成型介質(PID),通過光刻工藝制備SiC MOSFET功率器件電極上的互連盲孔;基于板級物理氣相沉積(PLPVD)技術批量更改SiC MOSFET等功率器件電極上的金屬;通過雙面再布線層(DSRDL)工藝替代功率器件的傳統(tǒng)鍵合技術。開發(fā)的新型有機基板埋入SiC MOSFET半橋功率模塊樣品厚度薄,體積遠小于傳統(tǒng)TO-247封裝(如圖1所示)。

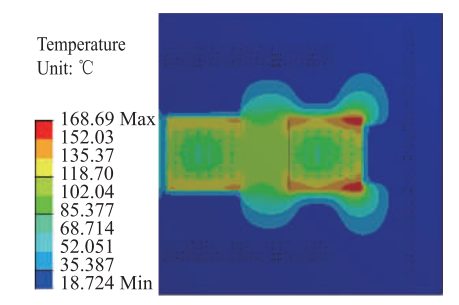

(a) 模擬芯片散熱情況

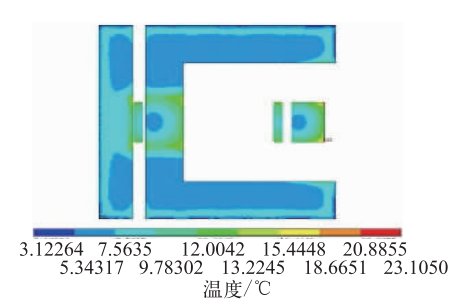

(b) RDL中的應力分布模擬

(c) 溫度等高線

(d) 應力等高線

(d) 應力等高線

(e) ACO-BPNN流程圖

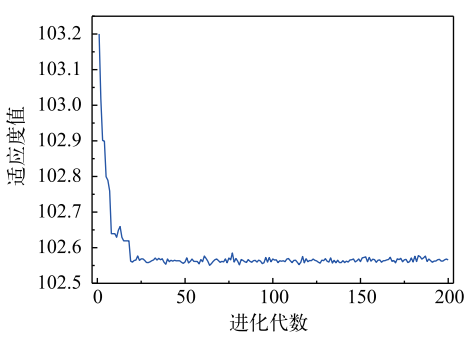

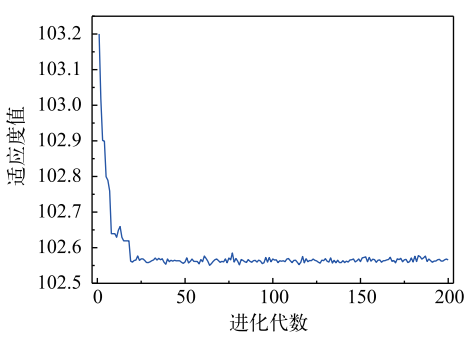

(f) 適應度曲線

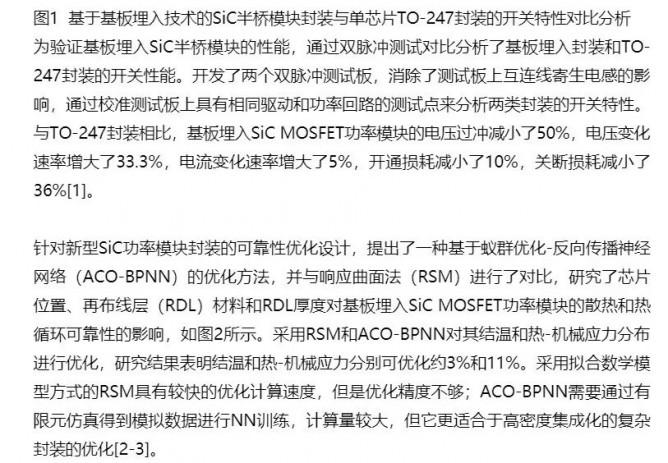

圖2 基于蟻群優(yōu)化-反向傳播神經(jīng)網(wǎng)絡算法的基板埋入式SiC功率模塊封裝可靠性優(yōu)化

原文文獻:

[1]HOU F Z, WANG W B, MA R, et al. Fan-out panel-level PCB embedded SiC power MOSFETs packaging[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 367-380.

[2]QIAN Y C, HOU F Z, FAN J J, et al. Design of a fan-out panel-level SiC MOSFET power module using ant colony optimization-back propagation neural network[J]. IEEE Transactions on Electron Devices, 2021, 68(7): 2021.

[3]樊嘉杰,錢弈晨. 一種高可靠性的嵌入式SiC功率器件封裝設計方法:ZL202110700564.6[P]. 2022-04-01.

來源:電子與封裝